Intel 4 и TSMC 3 нм: характеристики будущего техпроцесса

На днях состоялась презентация Intel, посвященная следующему техпроцессу компании. Главной новостью стало номинальное соблюдение требований закона Мура (эмпирического наблюдения, которого уже десятки лет стараются придерживаться производители процессоров) — двойное увеличение плотности размещения транзисторов. В самом законе речь идет о количестве транзисторов на кристалле интегральной схемы вообще, но для сравнения разных поколений и разных производителей лучше оперировать данными об удельной плотности размещения — т.е. количестве транзисторов на 1 мм2. Intel заявляет, что её следующий 4-нм техпроцесс от нынешнего 7-нм (который до ребрендинга назывался 10-нм) обеспечит как раз 2-кратной увеличение удельной плотности размещения транзисторов. Вот как выглядят ключевые параметры Intel 4 и его предшественников:

| Техпроцесс | 90 нм | 65 нм | 45 нм | 32 нм | 22 нм | 14 нм | Intel 7 (10 нм) | Intel 4 |

| Год выпуска | 2004 | 2006 | 2008 | 2010 | 2011 | 2014 | 2021 | 2023 |

| CPP | 260 нм | 220 нм | 180 нм | 112.5 нм | 90 нм | 70 нм | 60 нм | 50 нм |

| MMP | 220 нм | 210 нм | 160 нм | 112.5 нм | 80 нм | 52 нм | 40 нм | 30 нм |

| CPP x MMP | 57,200 нм² | 46,200 нм² | 28,800 нм² | 12,656 нм² | 7,200 нм² | 3,640 нм² | 2,400 нм² | 1,500 нм² |

| Уменьшение площади транзистора | 1.24x | 1.6x | 2.28x | 1.76x | 1.98x | 1.52x | 1.6x |

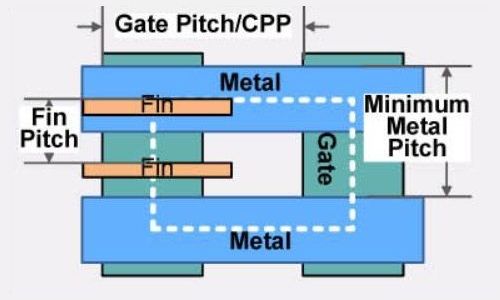

Как уже рассказывал Gadgets News, ключевыми параметрами транзистора, определяющими его площадь, являются шаг затвора, т.е. расстояние между соседними затворами (CPP) и шаг межсоединения, он же минимальный шаг дорожек металлического слоя (MMP). Ранее 10-нм техпроцессу Intel были обещаны CPP и MMP в размере 54 нм и 36 нм, что обеспечивало 1.87-кратное увеличение удельной плотности размещения транзисторов. Однако в обновленных данных наших коллеги из AnandTech фигурируют уже другие цифры — те, что вы можете видеть в таблице сверху. Согласно данной метрике (CPP x MMP), за 7 лет удельная плотность размещения транзисторов у Intel увеличилась всего в полтора раза — тогда как в соответствии с законом Мура она должны была удвоится уже к 2017 году. Немногим лучше выглядит переход от Intel 7 к Intel 4 — всего 1.6-кратное увеличение удельной плотности.

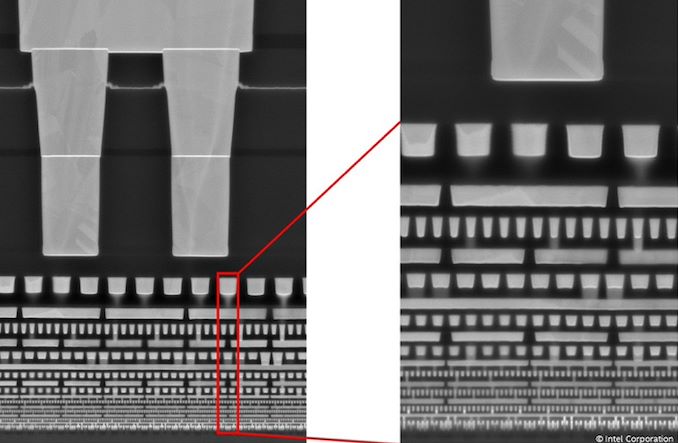

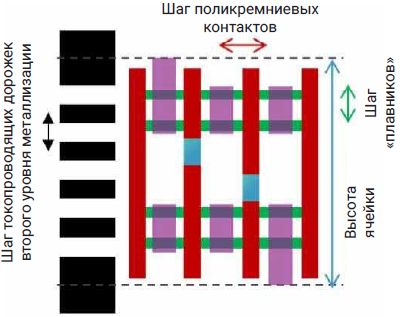

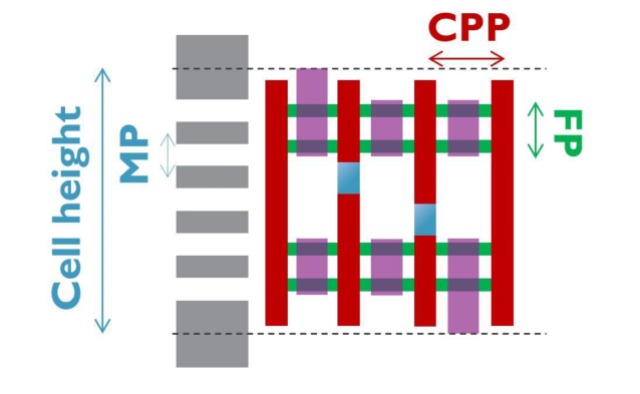

Однако с переходом на FinFET (начиная с 22-нм техпроцесса) логические элементы и ячейки памяти Intel стали иметь целые наборы рёбер. Например, у ячеек памяти SRAM на 22-нм техпроцессе имеется 14 рёбер, на 14-нм — 10 рёбер, на 10-нм — 8 рёбер. Соответственно Intel стала определять удельную плотность размещения транзисторов перемножением расстояния между соседними затворами (CPP) на т.н. «высоту» логического элемента (или ячейки памяти). В разных источниках она определяется либо количеством токопроводящих дорожек, либо количеством диэлектрических рёбер, умноженным на расстояние между ними (metal pitch или fin pitch соответственно). Почему этот параметр называется высотой не вполне понятно — транзисторы располагаются в двухмерной плоскости — вертикально, друг над другом, размещены металлические слои:

Итак, нынешняя метрика современного и будущего поколения техпроцесса Intel выглядит так:

| Intel 4 | Intel 7 | |

| Шаг затвора (расстояние между соседними затворами), CPP | 50 нм | 60 нм |

| Шаг межсоединения (расстояние между токопроводящими металлическими дорожками), MP | 30 нм | 40 нм |

| Шаг ребра (расстояние между диэлектрическими рёбрами), FP | 30 нм | 34 нм |

| Количество рёбер | 8 | 12 |

| Высота логического элемента | 240 нм | 408 нм |

| CPP x высота логического элемента | 12,000 нм2 | 24,480 нм2 |

В таблице выше высота ячейки определяется диэлектрическими ребрами (FP), а в схемах ниже (для 6T SRAM) — токопроводящими металлическими дорожками (межсоединениями, MP).

При таком методе измерения переход с Intel 7 на Intel 4 сопровождается уже двойным увеличением удельной плотности размещения транзисторов — как того и требует закон Мура. Согласно нашим коллегам из AnandTech, удельная плотность размещения транзисторов у техпроцесса Intel 7 составляет 80 млн / мм2. Это для HP, т.е. высокопроизводительных, библиотек (как и выкладки в таблице сверху). В этом случае Intel 4 будет иметь 160 млн / мм2. Для сравнения, площадь новейшего Apple M2, созданного на базе 2-го поколения TSMC 5 нм, оценивается некоторыми специалистами в 155 мм2, что при 20 млрд транзисторов дает удельную плотность почти в 130 млн / мм2.

Первые поставки процессоров на базе техпроцесса Intel 4 запланированы на 2023.

Своими планами на будущее поделилась и TSMC. Компания анонсировала сразу четыре модификации своего 3-нм техпроцесса, которые, в зависимости от требований заказчика, имеют разные характеристики по удельной плотности размещения транзисторов, тактовой частоте, энергопотреблению, стоимости. Однако количество транзисторов на мм2 у TSMC 3 нм (чей релиз также состоится в 2023 году) уменьшится не до 50% от нынешнего TSMC 5 нм (как того требует закон Мура), а в лучшем случае (N3E 2-1 Fin, т.е. двойной затвор и одно ребро) до 64%. По аналогии с Apple M2 это означает около 200 млн транзисторов на мм2. Правда, 64% — это средняя величина, рассчитанная из удельной плотности размещения транзисторов в логических элементах (50%), ячейках SRAM (70%) и аналоговых элементах (80%). Т.е. в отношении логических элементов закон Мура в TSMC пока соблюдается. Но куда хуже обстоят дела у TSMC 2 нм (2-я пол 2025) — на уровне 90%. Правда, в 2-нм техпроцессе на смену FinFet придет принципиально новая технология, GAAFET.