Продолжает ли действовать закон Мура: проверяем на цифрах

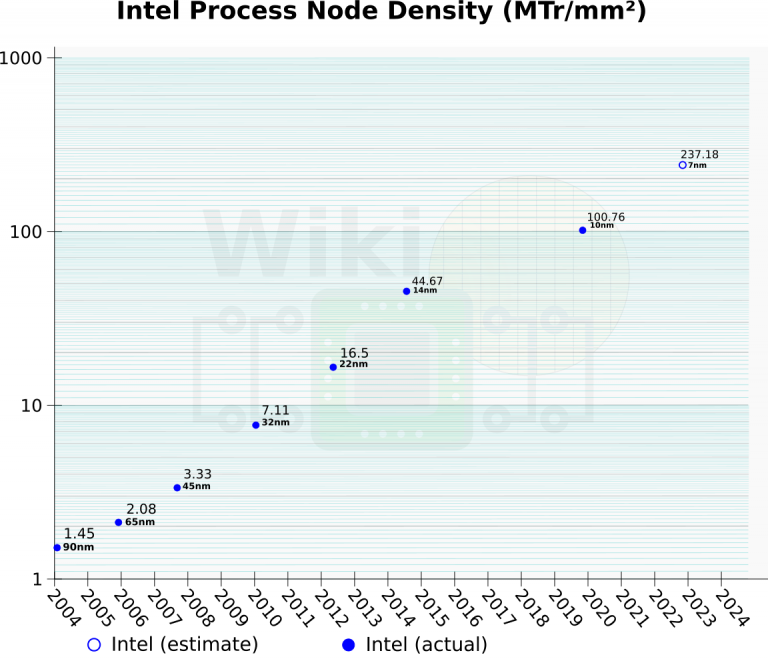

В последнее время немало говорят о том, что закон Мура (согласно которому количество транзисторов на кристалле интегральной схемы удваивается каждые два года), застопорился или даже вовсе перестал действовать. Причиной тому сильно задержанный релиз Intel процессоров с 10-нм литографией — изначально он был запланирован на 2015 год, но в конечном итоге перенесен на 2020.

И вот на днях наши коллеги из AnandTech подержали в руках полупроводниковую пластину Intel, изготовленную на базе 10-нм техпроцесса и содержащую процессоры с микроархитектурой новейшего поколения, Tiger Lake. По их прикидкам, процессор с этой пластины имеет площадь 146 мм². Из расчета заявленных Intel 100.8 млн транзисторов на 1 мм² получается, что общее количество транзисторов на кристалле процессора составляет около 14.7 млрд. Давайте попробуем оценить эти цифры на предмет выполнения закона Мура. Вот как выглядят характеристики дюжины процессоров Intel, начиная с самого первого:

| Процессор | Год выпуска | Кол-во транзисторов | Площадь кристалла |

| 4004 | 1971 | 2.3 тыс | 12 мм² |

| 8008 | 1972 | 3.5 тыс | 15 мм² |

| 8080 | 1974 | 6 тыс | 20 мм² |

| 80086 | 1978 | 29 тыс | 33 мм² |

| 80286 | 1982 | 134 тыс | 49 мм² |

| 80386 | 1985 | 275 тыс | 39 мм² |

| 80486 | 1989 | 1.18 млн | 81 мм² |

| Pentium | 1993 | 3.1 млн | 294 мм² |

| Pentium II | 1997 | 7.5 млн | 203 мм² |

| Pentium III | 1999 | 9.5 млн | 128 мм² |

| Pentium 4 | 2000 | 42 млн | 217 мм² |

| Core 2 Quad | 2007 | 582 млн | 286 мм² |

| Tiger Lake | 2020 | 14.7 млрд | 146 мм² |

По закону Мура, если взять за основу выпущенный в 1971 процессор Intel 4004 и удвоение его 2.3 тыс транзисторов каждые два года, к 2017 получается 19.3 млрд транзисторов. Это число вполне сопоставимо с оценкой количества транзисторов на кристалле процессора с архитектурой Tiger Lake, который таким образом запаздывает на три года. А вот в 2019 и 2021 расчетное, по закону Мура, количество транзисторов достигает гораздо более крупных величин — 38.6 и 77.2 млрд. Впрочем, если бы процессор с 10-нм техпроцессом и микроархитектурой Tiger Lake имел площадь как у Core 2 Quad (286 мм²), то достигнутое Intel количество транзисторов (28.8 млрд) стало сопоставимым с ожиданиями на 2019, и тогда отставание составляет всего один год.

Что касается дальнейших перспектив, то плотность размещения транзисторов у 7-нм техпроцесса (процессоры с которым появятся не раньше 2023) оценивается в 237 млн/мм². Соответственно на кристалле площадью 286 мм² число транзисторов достигнет 68.8 млрд — что снова близко к расчетной величине Мура в 2021 году.

Таким образом, хоронить закон Мура преждевременно — максимум речь идет о его небольшом замедлении, да и то в отношении непосредственно Intel. Процессоры с эквивалентным Intel 10 нм техпроцессом TSMC 7 нм (91 млн/мм²) появились еще в 2018. В этом году им на смену (по меньшей мере в отношении мобильных чипов Apple) придет TSMC 5 нм. Правда, у последнего плотность размещения транзисторов меньше предполагаемого Intel 7 нм — она составляет 173 млн/мм², зато с опережением графика Мура в один год.

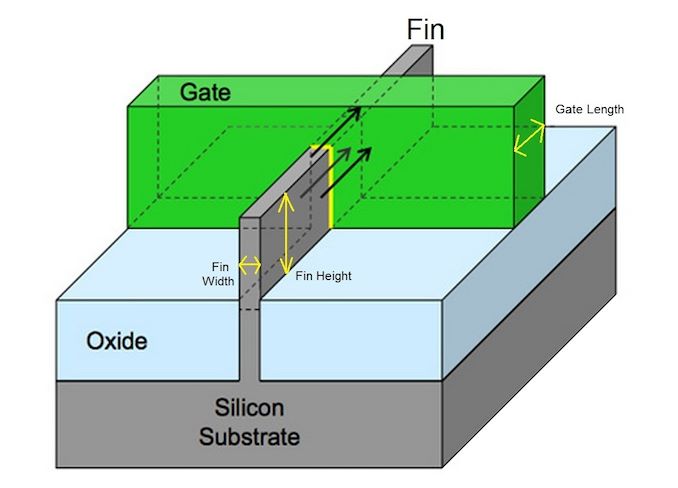

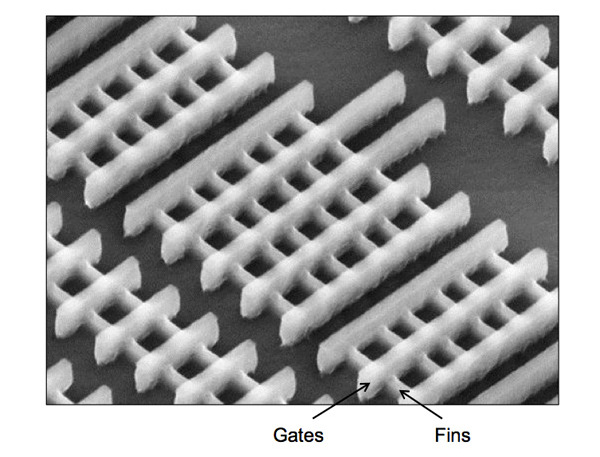

Уровень миниатюризации как таковой можно оценить по толщине токопроводящего ребра (fin width). Это самая маленькая размерность в транзисторной топологии, и она уже почти не меняется: 8 нм — в Intel 14 нм, 7 нм — в Intel 10 нм. Так же незначительно уменьшилась толщина затвора (gate length) — с 20 до 18 нм.

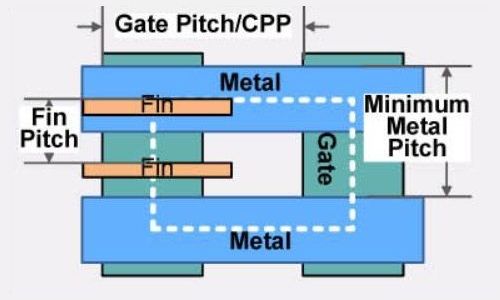

Вообще же главными параметрами, определяющими закон Мура, являются два следующих:

- шаг затвора, т.е. расстояние между соседними затворами (CPP)

- шаг межсоединения, он же минимальный шаг дорожек металлического слоя (MMP).

Собственно они, как стороны прямоугольника, и определяют площадь транзисторной ячейки. Для удвоения числа транзисторов на заданном кристалле их площадь должна сократиться вдвое, что означает уменьшение сторон транзисторной ячейки (CPP и MMP) до 70% от исходного размера (0.7 x 0.7 ≈ 0.5). И вот здесь изменения при переходе от 14-нм техпроцесса Intel к 10-нм уже более заметны: CPP уменьшился с 70 до 54 нм, MMP — с 52 до 36 нм. Получается 54/70 x 36/52, т.е. 0.77 x 0.69 = 0.534. Номинально это означает сокращение площади транзистора в 1.87 раз. Казалось бы налицо небольшое отставание от требуемого уменьшения в 2 раза, но если мы взглянем на динамику последних 15 лет, то там тоже все было не так радужно:

| Техпроцесс | 90 нм | 65 нм | 45 нм | 32 нм | 22 нм | 14 нм | 10 нм |

| Год выпуска | 2004 | 2006 | 2008 | 2010 | 2011 | 2014 | 2020 |

| CPP | 260 нм | 220 нм | 180 нм | 112.5 нм | 90 нм | 70 нм | 54 нм |

| MMP | 220 нм | 210 нм | 160 нм | 112.5 нм | 80 нм | 52 нм | 36 нм |

| CPP x MMP | 57,200 нм² | 46,200 нм² | 28,800 нм² | 12,656 нм² | 7,200 нм² | 3,640 нм² | 1,944 нм² |

| Уменьшение площади транзистора | 1.24x | 1.6x | 2.28x | 1.76x | 1.98x | 1.87x |

В том, что закон Мура приближается к своему пределу, мало кто сомневается — на каком-то уровне миниатюризации неизбежными становятся утечки тока. Пока с ними пытаются бороться при помощи применения новых транзисторных структур, например MBCFET. А главное производительность можно наращивать за счет объединения в один процессор нескольких кристаллов (чиплетов). Над подобными технологиями активно работает как Intel, так и AMD. Не будем сбрасывать со счетов и совсем уже оригинальные решения, вроде Cerebras WSE. Как рассказывал Gadgets News, он объединяет десятки чипов и триллион транзисторов непосредственно на полупроводниковой пластине диаметром 30 см.