Ponte Vecchio Xe-HPC: 100 млрд транзисторов и 1 Петафлопс производительности [обновлено]

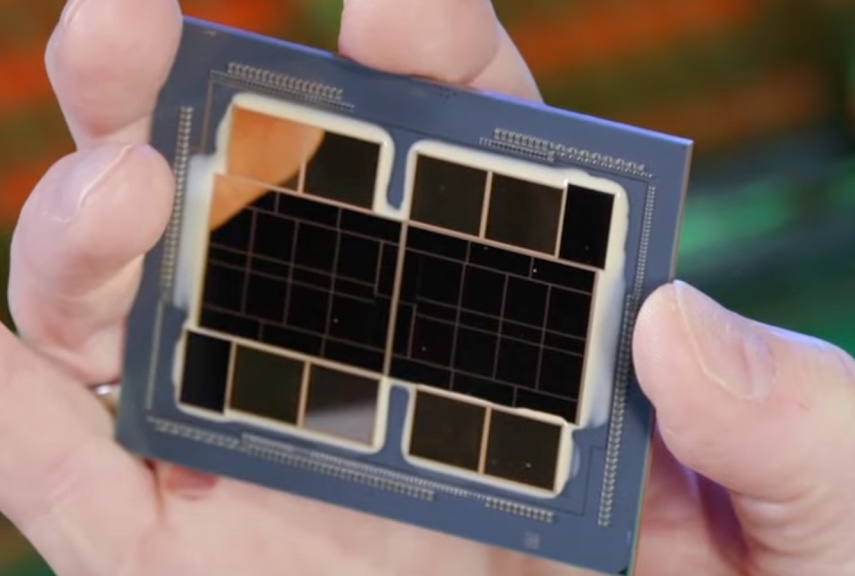

Сегодня Intel в очередной раз показала свой графический суперпроцессор Ponte Vecchio Xe-HPC и раскрыла о нем кое-какие подробности. Как уже рассказывал Gadgets News, осенью 2017 года Intel объявила о намерении заняться «топовыми решениями дискретной графики для широкого диапазона вычислительных сегментов», которые возглавил уволившийся из AMD Раджа Кодури. Позднее стало известно о делении будущих графических ускорителей на три категории: Xe-LP (для мобильных устройств, от смартфонов до ноутбуков), Xe-HP (для игровых ПК и рабочих станций) и Xe-HPC (для серверов и суперкомпьютеров). Последними, в частности, будет оснащен первый американский экзафлопсный суперкомпьютер, запуск которого запланирован на 2022 год. Примерно год назад Intel показала графический чип огромного размера «со многими десятками миллиардов транзисторов», а сегодня подробно описала его структуру.

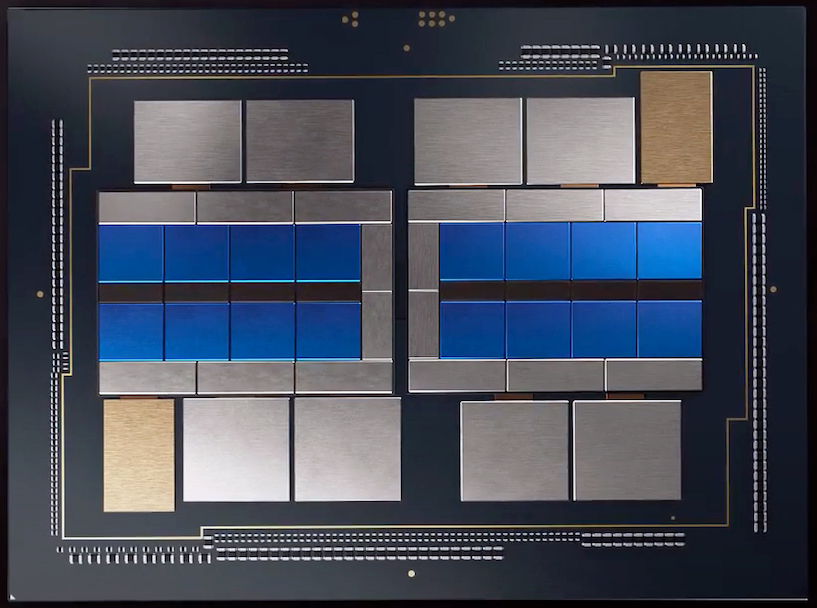

ГПУ насчитывает множество небольших чиплетов. Сама Intel сообщает о 47 «магических плитках» (согласно Tom’s Hardware):

- 2 базовые плитки на основе 10-нм техпроцесса Intel (SuperFin)

- 16 вычислительных плиток — изначально на основе 5-нм (?) техпроцесса TSMC, с последующим переходом на 7-нм техпроцесс Intel (предположительно в 2023 году)

- 8 плиток с кешом Rambo на основе 10-нм техпроцесса Intel (SuperFin)

- 11 соединительных мостов EMIB, сделанных Intel

- 2 интерфейсных контроллера Xe I/O

- 8 модулей памяти HBM.

Общее количество транзисторов на этом огромном ГПУ превышает 100 млрд. Для сравнения, монолитный 7-нм кристалл ГПУ Nvidia A100 имеет 54 млрд транзисторов на 826 мм2, а девять чиплетов (восемь 7-нм для вычислений, один 14-нм в качестве интерфейсного контроллера) на 1000 мм2 64-ядерного процессора AMD EPYC 7742 — 32 млрд транзисторов.

Заявленная Intel производительность Ponte Vecchio Xe-HPC — 1 PFLOPS с точностью FP16. Половинная точность вполне уместна в машинном обучении, но при этом следует помнить, что в рейтинге суперкомпьютеров традиционно применяется двойная (FP64). Для сравнения, вышеупомянутый графический ускоритель Nvidia A100 выдает 78 TFLOPS FP16. Единственным разумным объяснением почти 13-кратной разницы в скорости при 2-кратной разнице в количестве транзисторов является специфический вид вычислений, в которых достигается скорость в 1 PFLOPS. В частности, в тензорный вычислениях на разреженных (с преимущественно нулевыми элементами) матрицах быстродействие Nvidia A100 взлетает до 312 TFLOPS — а это всего втрое меньше 1 PFLOPS у Ponte Vecchio Xe-HPC.

ОБНОВЛЕНИЕ

Сообщается, что энергопотребление Ponte Vecchio Xe-HPC составит 600 Вт, а его система охлаждения будет жидкостной. Экзафлопсный суперкомпьютер Aurora будет состоять из 9 тыс узлов, каждый из которых представлен двумя серверными процессорами Intel Xeon Scalable и шестеркой графических ускорителей Ponte Vecchio. Из расчета заявленного Intel быстродействия Ponte Vecchio Xe-HPC получается, что совокупная производительность ГПУ в суперкомпьютере составит 9000 x 6 x 1 PFLOPS FP16, т.е. 54 тыс PFLOPS FP16. Номинально это составляет 13.5 EFLOPS FP64 — при том, что заявленная производительность суперкомпьютера на порядок меньше. Из чего можно заключить, что реальная скорость Ponte Vecchio Xe-HPC в операциях с плавающей точкой находится на уровне 100 TFLOPS FP16.