Подробности о 10-нм техпроцессе Intel

Вчера состоялась большая презентация Intel, посвященная её технологическим процессам, в т.ч. 10-нанометровому, релиз которого ожидается в конце этого года. Это чрезвычайно занимательная тема — как с точки зрения будущих перспектив закона Мура (согласно которому количество транзисторов на квадратном дюйме кристалла удваивается каждые два года), так и с точки зрения обозначения. Как мы уже неоднократно говорили, понятия «14-нанометровый» или «10-нанометровый» в значительной мере условны, разнятся между производителями чипов и даже не соответствуют фактическим размерам компонентов транзистора, созданного на базе этого техпроцесса. Последний казус лучше всего иллюстрируют официальные слайды самой Intel, на основе которых я подготовил эту таблицу:

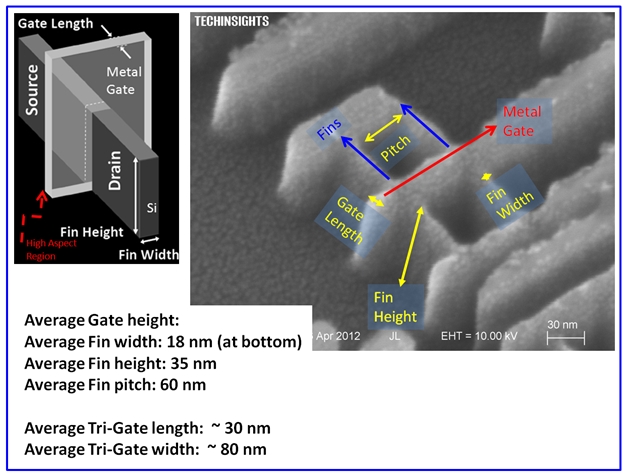

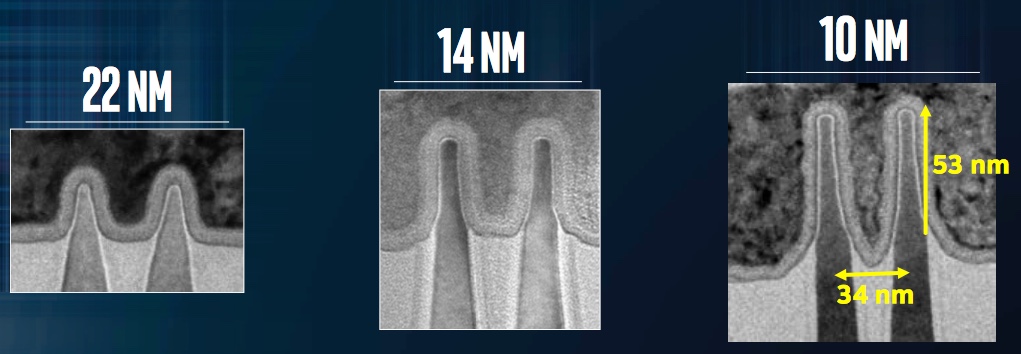

| 22-нм | 14-нм | 10-нм | |

| Logic cell height | 840 нм | 399 нм | 272 нм |

| Interconnect pitch (min metal pitch) | 80 нм | 52 нм | 36 нм |

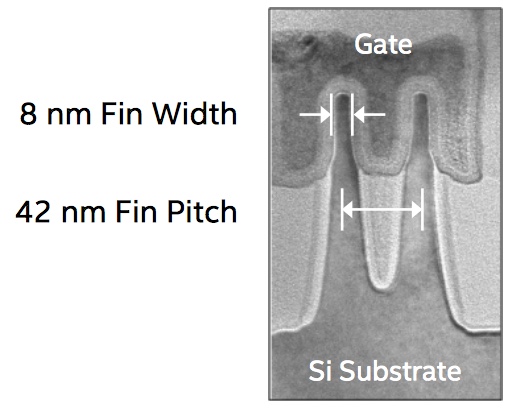

| Fin pitch | 60 нм | 42 нм | 34 нм |

| Fin height | 34 нм | 42 нм | 53 нм |

| Fin width | 18 нм | 8 нм | ? |

| Gate pitch | 90 нм | 70 нм | 54 нм |

| Gate length | 30 нм | 20 нм | ? |

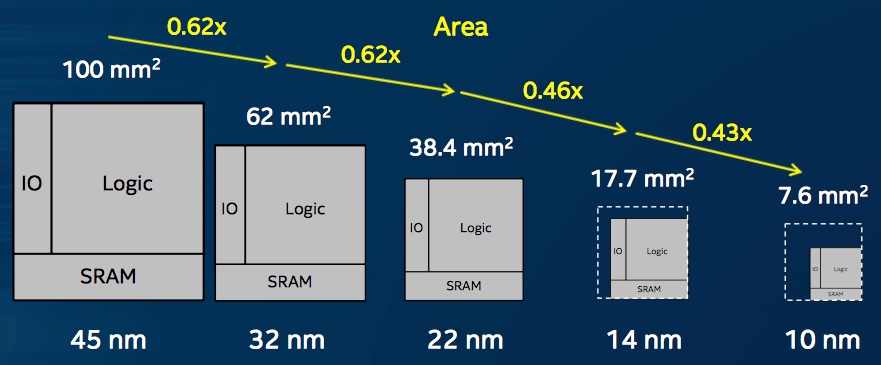

| Площадь интегральной схемы | 38.4 мм2 | 17.7 мм2 | 7.6 мм2 |

- Logic cell height — высота логической ячейки;

- Interconnect pitch — шаг межсоединения (минимальное расстояние между слоями внутрисхемных соединений);

- Fin pitch — шаг ребра (расстояние между диэлектрическими ребрами, проходящими перпендикулярно металлическому затвору);

- Fin height — высота ребер;

- Fin width — ширина ребер;

- Gate pitch — шаг затвора (расстояние между затворами соседних транзисторов, включая ширину самих затворов);

- Gate length — длина (толщина) затвора.

Именно длину затвора и принято считать узким местом техпроцесса, определяющим пределы закона Мура. Поэтому когда мы слышим, что он перестанет действовать после достижения 5-нанометрового техпроцесса, это не совсем корректно. Название техпроцесса, как мы уже говорили условно — в действительности туннельный эффект начнет сказываться когда 5 нанометров достигнет непосредственно длина затвора. К сожалению, мы пока не располагаем данными о длине затвора в 10-нанометровом техпроцессе и не можем оценить насколько он стал ближе к 5-нанометровому пределу.

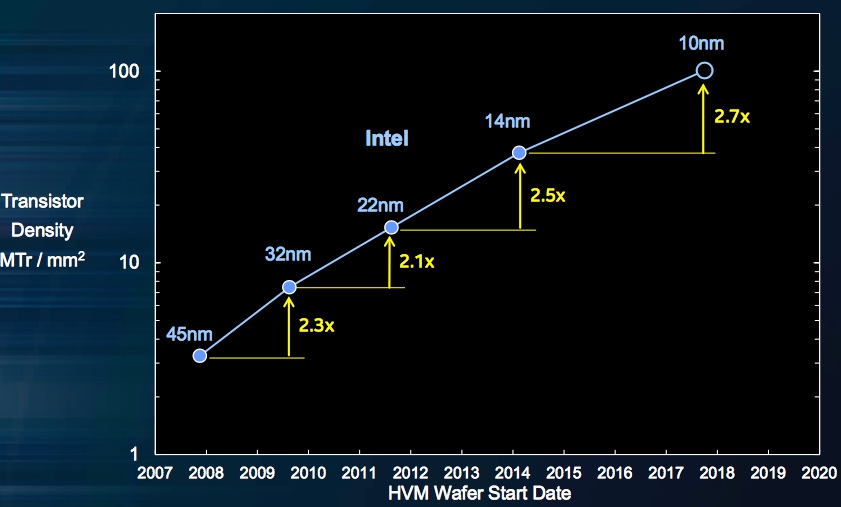

Несмотря на ранее высказанные опасения, что закон Мура дает сбой (во всяком случае в Intel), компания в своих слайдах демонстрирует, что по-прежнему ему следует:

Из этого графика видно, что хотя периоды между техпроцессами увеличиваются, одновременно с этим растет темп увеличения плотности размещения транзисторов на кристалле. С конца 2007 года (45-нм техпроцесс), когда она составляла 5 млн. транзисторов на мм2, плотность вырастет до 100 млн. в конце 2017 года, когда начнется массовое производство процессоров с 10-нм литографией. Таким образом, количество транзисторов за 10 лет выросло в 20 раз. Это не вполне соответствует закону Мура, но и не так чтобы сильно от него отстает:

- 2008 — 5 млн.

- 2010 — 10 млн.

- 2012 — 20 млн.

- 2014 — 40 млн.

- 2016 — 80 млн.

- 2018 — 160 млн.

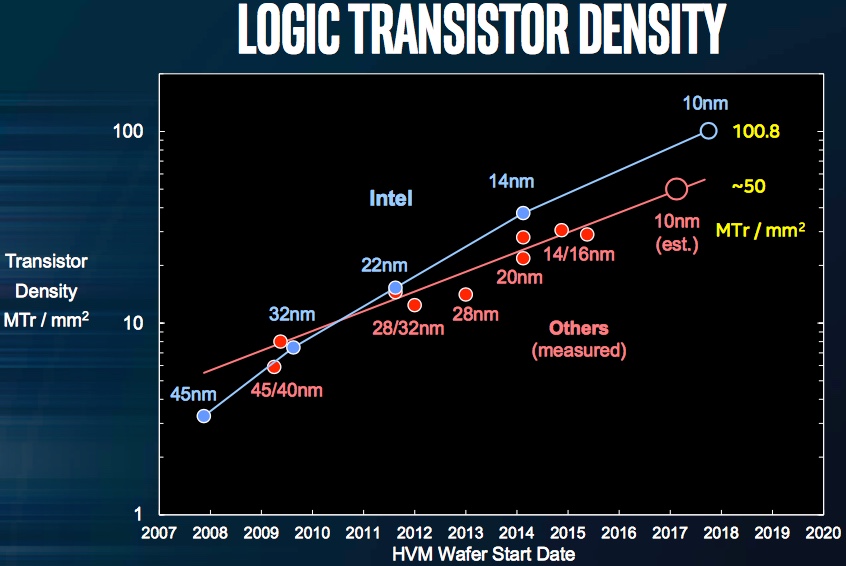

В своей презентации Intel затронула и такой злободневный вопрос как обозначение техпроцесса. Исторически каждый успешный переход обозначался числом, которое в 0.7 раз меньше предшествующего — 45 нм, 32 нм, 22 нм, 16/14 нм, 10 нм. Сама Intel оценивала техпроцесс по двум метрикам:

- {Gate pitch} x {Interconnect pitch}, либо

- {Gate pitch} x {Logic cell height}.

Однако у них есть серьезный недостаток: они оторвались от главного критерия, по которому оценивается соблюдение закона Мура — плотности размещения транзисторов. Согласно слайдам с презентации Intel, у других производителей процессоров, перешедших на «10-нанометровый» техпроцесс (очевидно речь идет о Samsung и/или TSMS) плотность размещения транзисторов с элементарной логикой в два(!) раза меньше, чем у Intel.

Вместе с тем просто брать количество транзисторов и делить его на площадь кристалла Intel также считает не вполне корректным — такой подход не учитывает нюансы, связанные с архитектурой процессора (например, размер кэша). Компания предлагает вернуться к методу, который применялся несколько поколений техпроцесса назад. Его суть состоит в использовании суммы двух параметров:

- плотности размещения транзисторов c триггерной логикой (количество ÷ площадь), взятой с коэффициентом 0.4;

- плотности размещения транзисторов c NAND(И-НЕ)-логикой (количество ÷ площадь), взятой с коэффициентом 0.6.

Intel рекомендует производителям процессоров раскрывать плотность размещения транзисторов на мм2, и дополнительной к ней — размеры ячейки памяти SRAM.

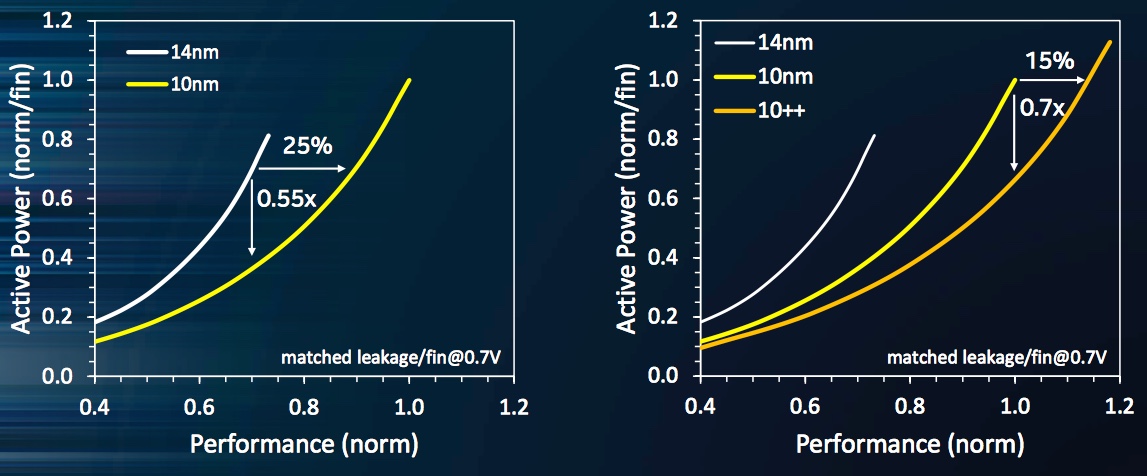

Но как бы интересны ни были вопросы техпроцесса, потребителей в первую очередь интересуют конкретные результаты от перехода с 14-нанометрового техпроцесса на 10-нанометровый. Так вот согласно Intel при одинаковом уровне энергопотребления (и очевидно прочих равных условиях — архитектуре, тактовой частоте и т.д.) только за счет нового техпроцесса производительность вырастет на 25% — или при заданном уровне производительности энергопотребление уменьшится почти в два раза. В свою очередь у 3-го поколения 10-нанометрового техпроцесса (10++) еще на 15% вырастет производительность или на 30% уменьшится энергопотребление.

Массовое производство чипов Intel с 10-нанометровой архитектурой стартует в конце нынешнего года.